If you’re in the market for a re-programmable cryptocurrency miner, look no further. UltraMiner FPGA delivers power, efficiency, and convenience at an affordable price. And if you don’t want to mine crypto, but you do want a development board that showcases not only the prototyping potential but also the speed of a modern FPGA, then you too have come to the right campaign.

Below are a few of UltraMiner’s key features:

Building a mining rig around a Graphics Processing Unit (GPU) can be fun, but GPUs are designed to power computer displays, not mining algorithms. Turning one into a functional miner requires that you invest in an entire PC setup. At a minimum, that includes the CPU, the memory, a hard drive, a motherboard with PCIe support, and a power supply. Each of these components increases the cost of your rig and expands its footprint. And because modern GPUs have thousands of cores, and are designed to consume as much power as possible in order to outperform their competitors, your reward for all of this work is a flaky, inefficient miner that’s prone to overheating.

Custom-built Application Specific Integrated Circuit (ASIC) rigs are the gold standard for cryptocurrency mining. They are quite expensive, however, and they only work on the algorithms for which they were designed. You can think of an FPGA as a reconfigurable ASIC. With the right algorithm implementation, an FPGA can match the efficiency of an ASIC miner, which is often about ten times the performance-per-Watt of a GPU rig. Better yet, your FPGA miner won’t turn into a paperweight if the algorithm for the cryptocurrency you are mining is updated or if you decide to start mining something else.

And because UltraMiner is designed to be a standalone device, it does not require that you invest in a desk full of peripheral components. Its small form factor and flexible cooling options allow you to set it up and plug it in virtually anywhere. This is already true of the UltraMiner prototype shown below:

And we’ve optimized the latest design to support a somewhat less imposing CPU cooler:

UltraMiner is equipped with the latest Kintex UltraScale+ KU3P FPGA, which is from the same TSMC FinFET 16 nm process technology that powers the Bitmain Miner S9 ASIC miner. UltraMiner can achieve ASIC-like mining performance at one quarter of a GPU miner’s power consumption.

| UltraMiner FPGA | Typical FPGA Miner | GPU | CPU | |

|---|---|---|---|---|

| Performance | High | High | Medium | Low |

| Power Efficiency | High | High | Medium | Low |

| Power Consumption | 50 W | 50 W - 2000 W * | 200 W | 150 W |

| Heat & Noise | Low | Low | High | High |

| Open Source | Yes | No | Partial | Yes |

| Price | $399 | $200-$4000 * | $500 ** | $200 ** |

| Algorithm Adaptation | Intermediate | Slow | Intermediate | Fast |

* - Depends on the specific model. See the following table for more detail

** - Device alone. Does not include the cost of peripherals

UltraMiner supports multiple cryptocurrency mining algorithms. We have already developed and validated several using our prototype boards, and we plan to develop more. When we do, we will publish them free of charge.

| UltraMiner Hash Performance | UltraMiner Power Consumption | GPU Hash Performance | GPU Power Consumption | |

|---|---|---|---|---|

| 0xBitcoin | 2.7 Gh/s | 60 W | 1.5 Gh/s | 200 W |

| 2.1 Gh/s * | 20 W | - | ||

| ODOCrypt (digiByte) | 420 Mh/s | 50 W | N/A | N/A |

| 320 Mh/s * | 20 W | - | ||

| Keccak (Max, SMART) | 2.7 Gh/s | 60 W | 1.5 Gh/s | 200 W |

| 2.1 Gh/s * | 20 W | - | ||

| ZP (ZenProtocol) | 2.7 Gh/s | 60 W | 1.5 Gh/s | 200 W |

| 2.1 Gh/s * | 20 W | - | ||

| SHA256T (OCP) | Estimated 2 Gh/s | 45 W | - | - |

| SHA256-Amoveo (Amoveo) | Estimated 2.4 Gh/s | 45 W | - | - |

| BSHA3 | Estimated 1.3 Mh/s | 50 W | - | - |

* - UltraMiner supports dual voltage operation (0.85 V or 0.75 V)

UltraMiner comes with full-featured power and frequency-control software that can dynamically update the FPGA’s core voltage and core hash frequency, allowing you to find the perfect balance between performance and energy efficiency. The KU3P supports a wide core voltage range, as well. Working with a Keccak (SHA-3) mining algorithm, our internal test results show that increasing core voltage to 0.95 V, from the nominal 0.85 V, boosts performance by almost 25%:

| Voltage | Frequency |

|---|---|

| 0.85 V | 700 Mhz |

| 0.95 V | 870 MHz |

This works in the other direction as well. Decreasing supply voltage to 0.65 V reduces power consumption by over 45% without a significant drop in mining performance:

| Voltage | Power |

|---|---|

| 0.85 V | 38 W |

| 0.65 V | 20.7 W |

We are fed up with closed mining projects that benefit only a select few and with companies that demand license fees for periodic bitstream updates. We seek to provide an alternative to both. We support the open source movement, particularly within the crypto-mining community, where openness and transparency are key foundational principles. In order to help strengthen that community, we intend to open source:

With the source code package we provided, you can easily build a mining algorithm like the one shown below:

| UltraMiner FPGA | BCU1525 (VCU1525 Mod) | F1+ BlackMiner | F1 MINI | GPU GTX1070 | |

|---|---|---|---|---|---|

| Form Factor | Small | Large | Bulky | Small | Medium |

| Easy of Configuration | Home Friendly | Professional | Professional | Home Friendly | Hobbyist |

| Chipset | Kintex UltraScale+ | Virtex UltraScale+ | Kintex 7 | Kintex 7 | GTX1070 |

| Logic Resources | 356 K | 2.59 M | 326 K x 12 | 326 K | 356 K |

| Process Technology | 16 nm | 16 nm | 28 nm | 28 nm | 16 nm |

| Hash Performance (Keccak) | 2.7 Gh/s | 18 Gh/s | 32 Gh/s | 1.95 Gh/s | 500 Mh/s |

| Power Consumption (Keccak) | 50 W | 350 W | 1050 W | 50 W | 100 W |

| Open Source | Yes | No | No | No | Yes |

| Supportive Documents | Full | Limited | No | No | Full |

| Development Suite | Free | Device Locked | $2,000 | $2,000 | Free |

| Clock/Voltage Control | Dynamic | Limited | Controlled | Controlled | Dynamic |

| Full Featured Software | Yes | Limited | Controlled | Controlled | Yes |

| Main Interface | USB, GPIO, (Optional PCIe) | USB, PCIe | Ethernet | Ethernet | PCIe |

| Development Usage | Yes | Yes | No | No | Yes |

| Price | $399 | $3,945 | $2,350 | $179 | $499 |

| Connector 1 (3.3 V) | Connector 2 (1.8 V) |

| Pins | Pins | |||||||

|---|---|---|---|---|---|---|---|---|

| 3.3 V | 1 | 2 | 5 V | 1.8V | 1 | 2 | 1.8 V | |

| GPIO 01 | 3 | 4 | GND | 1N | 3 | 4 | GND | |

| GPIO 02 | 5 | 6 | GPIO 18 | 1P | 5 | 6 | 8N | |

| GPIO 03 | 7 | 8 | GPIO 17 | GND | 7 | 8 | 8P | |

| GND | 9 | 10 | GPIO 16 | 2N | 9 | 10 | GND | |

| GPIO 04 | 11 | 12 | GND | 2P | 11 | 12 | 7N | |

| GPIO 05 | 13 | 14 | GPIO 15 | GND | 13 | 14 | 7P | |

| GPIO 06 | 15 | 16 | GPIO 14 | 3N | 15 | 16 | GND | |

| 3.3 V | 17 | 18 | GPIO 13 | 3P | 17 | 18 | 6N | |

| GPIO 07 | 19 | 20 | GND | GND | 19 | 20 | 6P | |

| GPIO 08 | 21 | 22 | GPIO 12 | 4N | 21 | 22 | GND | |

| GPIO 09 | 23 | 24 | GPIO 11 | 4P | 23 | 24 | 5N | |

| GND | 25 | 26 | GPIO 10 | GND | 25 | 26 | 5P |

Whereas most affordable FPGA development boards are designed with Xilinx 7 Series (Artix-7 and Kintex-7) chips from 2010, UltraMiner is built around the latest Kintex UltraScale+ FPGA, which is two generations newer. The high performance, low-power semiconductor process of the Xilinx UltraScale+ (TSMC 16 nm FinFET+) yields between 2 and 2.4 times the performance-per-Watt of the Kintex-7’s 28 nm process nodes:

| 16 nm UltraScale+ Vmin | 16 nm UltraScale+ Vnom | 20 nm UltraScale Vnom | 28 nm 7 Series Vnom | |

|---|---|---|---|---|

| Operating Voltage (VCCINT) | 0.72 V | 0.85 V | 0.95 V | 1 V |

| Normalized Fabric Performance | 1.2x | 1.6x | 1.2 V | 1.0x |

| Normalized Total Power | 0.5x | 0.8x | 0.7x | 1.0x |

| Performance/Watt | 2.4x | 2x | 1.7x | 1.0x |

Our own internal testing shows performance gains and power savings that are even better than the manufacturer’s marketing data. The same implementation of the Keccak (SHA-3) hash algorithm ran 82% faster on a KU3P than it did on a 7-series Kintex with similar logic resources, all while consuming 36% less power:

| KU3P | Kintex-7 | |

|---|---|---|

| Frequency | 800 MHz | 440 MHz |

| Power | 9.6 W | 15 W |

UltraMiner includes a powerful TI PMIC that can supply up to 60 A to its core power rail. That’s three times the load of a typical FPGA dev board. As with other computationally intensive FPGA designs, power is central to cryptocurrency mining. Due to the high resource utilization rate of our designs (sometimes up to 95% LUT utilization), we found ourselves constantly running up against the limitations of our on-board PMIC.

Internal testing showed that designs running on the UltraMiner prototype – with full FPGA resource utilization and at the maximum PLL frequency of 900 MHz – required more than 50 A on the core FPGA power rail, but we struggled to find an FPGA dev board with a PMIC that could provide more than 30 A of current load. So we made our own. With UltraMiner, not a single hardware resource will go to waste due to the limitations of your power supply.

UltraMiner’s PMIC also supports dynamic voltage output monitoring and adjustment. This feature is quite powerful when combined with the benefits of the TSMC 16 nm FinFET+ process, which allows the UltraMiner’s KU3P to operate at different supply voltages depending on the requirements of a particular application. For the absolute best performance, you can operate the devices at its nominal supply voltage of 0.85 V, but applications with tighter power constraints can operate at 0.75 V while consuming up to 30% less power.

UltraMiner’s KU3P is one of only two FPGA models in the UltraScale+ family for which Xilinx provides a free license to use the full-featured WebPACK version of its Vivado design suite.

If you want to learn how to program UltraScale+ hardware – which is widely used in industrial and scientific applications due to its feature set and performance characteristics – UltraMiner is likely your most affordable option. And even if you’re not an RTL programmer, that Vivado license can still help you out:

"Vivado High-Level Synthesis, included as a no cost upgrade in all

Vivado HLx Editions, accelerates IP creation by enabling C, C++ and

System C specifications to be directly targeted into Xilinx

programmable devices without the need to manually create RTL."

In today’s market, FPGA manufacturers have a great deal of control over the prices at which global distributors can sell their chips. As you can see in the comparison table below, most UltraScale+ FPGA boards are outrageously expensive. We have gone through a long process of negotiation – both with our supplier and with Xilinx – to reach a price point for the KU3P that allows us to keep UltraMiner affordable. We were able to do so in part because of demand within the cryptocurrency community and among FPGA developers.

| UltraMiner FPGA | KCU116 | TE0841 | Genesys 2 | Nexys 4 | |

|---|---|---|---|---|---|

| Manufacturer | Agilmine | Xilinx | Trenz | Digilent | Digilent |

| FPGA family | Kintex UltraScale+ | Kintex UltraScale+ | Kintex UltraScale | 7 Series Kintex | 7 Series Artix |

| Model | KU3P | KU5P | KU035 | XC7K325T | XC7A200T |

| Logic Cell | 356 K | 475 K | 444 K | 326 K | 101 K |

| DSP Slices | 1368 | 1824 | 1700 | 840 | 240 |

| Block RAM | 12.7 Mb | 16.9 Mb | 19.0 Mb | 15.6 Mb | 4.74 Mb |

| UltraRAM | 13.5 Mb | 18.0 Mb | 0 | 0 | 0 |

| Max Power | 60 W | 20 W | 40 W | 20 W | 20 W |

| Price | $499 (Standard Edition $399) | $2995 | $1322 | $999 | $320 |

Whatever your FPGA design project might be – whether it’s related to crypto-mining, software-defined radio, cryptography, machine learning, or some other high performance application – a Kintex UltraScale+ FPGA can help you turn the crank more times per second. In fact, depending on the nature of that application, you might find yourself out-pacing the GPIO and MicroUSB interfaces on the Standard Edition of UltraMiner.

If IO bandwidth is a priority for you, have a look at our Developer Edition, which includes support for PCIe x4 Gen 3 and 100 high speed GPIOs broken out to standard-pitch headers. The Developer Edition of UltraMiner is perfect for designing PCIe-based solutions (and Xilinx has plenty of PCIe-related IP for you to explore). Or you can design your own high-performance DSP core. With enough IOs connected to an all-in-one ADC/DAC chip like the AD9363, UltraMiner’s UltraScale+ FPGA is just what your SDR project needs.

| Connector 1 (3.3 V) | Connector 2 (1.8 V) |

| Pins | Pins | |||||||

|---|---|---|---|---|---|---|---|---|

| 3.3 V | 1 | 2 | 5 V | 1.8V | 1 | 2 | 1.8 V | |

| GPIO 01 | 3 | 4 | GND | 1N | 3 | 4 | GND | |

| GPIO 02 | 5 | 6 | GPIO 18 | 1P | 5 | 6 | 8N | |

| GPIO 03 | 7 | 8 | GPIO 17 | GND | 7 | 8 | 8P | |

| GND | 9 | 10 | GPIO 16 | 2N | 9 | 10 | GND | |

| GPIO 04 | 11 | 12 | GND | 2P | 11 | 12 | 7N | |

| GPIO 05 | 13 | 14 | GPIO 15 | GND | 13 | 14 | 7P | |

| GPIO 06 | 15 | 16 | GPIO 14 | 3N | 15 | 16 | GND | |

| 3.3 V | 17 | 18 | GPIO 13 | 3P | 17 | 18 | 6N | |

| GPIO 07 | 19 | 20 | GND | GND | 19 | 20 | 6P | |

| GPIO 08 | 21 | 22 | GPIO 12 | 4N | 21 | 22 | GND | |

| GPIO 09 | 23 | 24 | GPIO 11 | 4P | 23 | 24 | 5N | |

| GND | 25 | 26 | GPIO 10 | GND | 25 | 26 | 5P |

| Connector 3 (1.8 V) | Connector 4 (3.3 V) |

| Pins | Pins | |||||||

|---|---|---|---|---|---|---|---|---|

| 1.8 V | 1 | 2 | 1.8 V | 3.3 V | 1 | 2 | 3.3 V | |

| 9N | 3 | 4 | GND | 17N | 3 | 4 | GND | |

| 9P | 5 | 6 | 16N | 17P | 5 | 6 | 24N | |

| GND | 7 | 8 | 16P | GND | 7 | 8 | 24P | |

| 10N | 9 | 10 | GND | 18N | 9 | 10 | GND | |

| 10P | 11 | 12 | 15N | 18P | 11 | 12 | 23N | |

| GND | 13 | 14 | 15P | GND | 13 | 14 | 23P | |

| 11N | 15 | 16 | GND | 19N | 15 | 16 | GND | |

| 11P | 17 | 18 | 14N | 19P | 17 | 18 | 22N | |

| GND | 19 | 20 | 14P | GND | 19 | 20 | 22P | |

| 12N | 21 | 22 | GND | 20N | 21 | 22 | GND | |

| 12P | 23 | 24 | 13N | 20P | 23 | 24 | 21N | |

| GND | 25 | 26 | 13P | GND | 25 | 26 | 21P |

| Connector 5 (3.3 V) | Connector 6 (1.8 V) |

| Pins | Pins | |||||||

|---|---|---|---|---|---|---|---|---|

| 3.3 V | 1 | 2 | 3.3 V | 1.8 V | 1 | 2 | 5 V | |

| 25N | 3 | 4 | GND | GPIO 19 | 3 | 4 | GND | |

| 25P | 5 | 6 | 32N | GPIO 20 | 5 | 6 | GPIO 36 | |

| GND | 7 | 8 | 32P | GPIO 21 | 7 | 8 | GPIO 35 | |

| 26N | 9 | 10 | GND | GND | 9 | 10 | GPIO 34 | |

| 26P | 11 | 12 | 31N | GPIO 22 | 11 | 12 | GND | |

| GND | 13 | 14 | 31P | GPIO 23 | 13 | 14 | GPIO 33 | |

| 27N | 15 | 16 | GND | GPIO 24 | 15 | 16 | GPIO 32 | |

| 27P | 17 | 18 | 30N | 1.8 V | 17 | 18 | GPIO 31 | |

| GND | 19 | 20 | 30P | GPIO 25 | 19 | 20 | GND | |

| 28N | 21 | 22 | GND | GPIO 26 | 21 | 22 | GPIO 30 | |

| 28P | 23 | 24 | 29N | GPIO 27 | 23 | 24 | GPIO 29 | |

| GND | 25 | 26 | 29P | GND | 25 | 26 | GPIO 28 |

Note: Open-source software and libraries provided to support the hardware modules in green

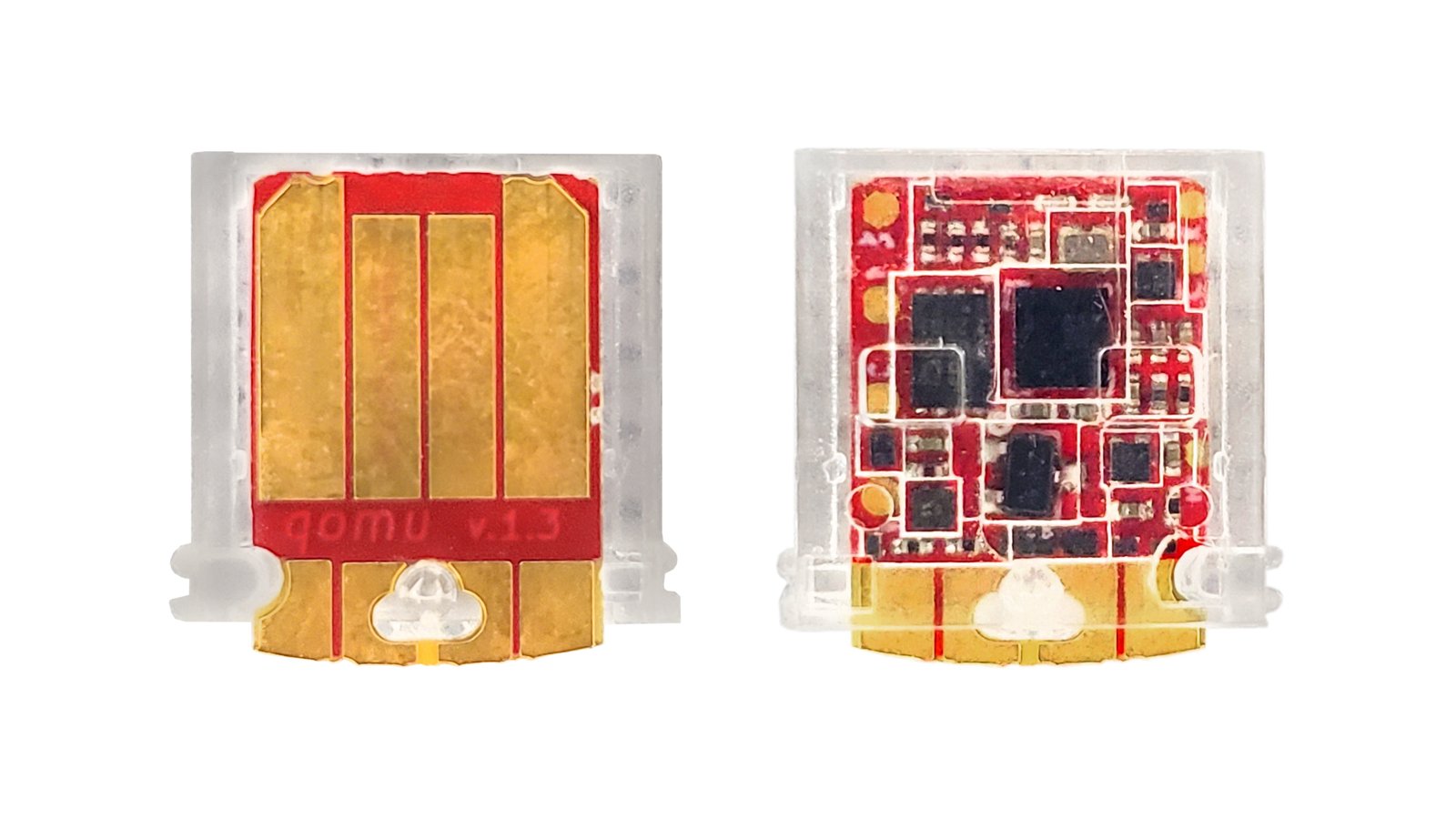

UltraMiner has passed the Engineering Validation Test (EVT) stage, which means that our engineering prototype is built, and major functionality has been validated. Our engineering work is not 100% complete, however. To facilitate easier testing, the current design routes all IO from the FPGA through the FPGA Mezzanine Card (FMC) connector.

In the next stage – Design Validation Testing (DVT) – we will produce a new prototype with PCIe and GPIO breakout connectors. That design will be identical to the final product outlined on our campaign page. This is a very low risk update, comparable to design changes that our team has made dozens of times before. Beyond that, our only planned modifications are minor optimizations and cost reduction efforts.

UltraMiner boards will be manufactured in Colorado, USA. AAPCB produced the prototype shown on the campaign page, and we have partnered with them for years. Together, we have a proven track record of delivering results on time. We have also partnered with factories in Portland, Oregon, so we have a backup plan if we run up against scheduling conflicts with AAPCB.

The advantage of manufacturing in the US is that we can attend to any issues in timely fashion and without worrying about customs paperwork and trade relations between the US and China. The downside of this decision is a higher cost per board and a longer turnaround time. If there is enough interest in UltraMiner – likely over 500 orders – we may consider moving the PCB production to China and only having the final boards assembled in the US (as our FPGA supplier is US-based).

We anticipate spending about two months in the DVT phase before going into production, which should take about another two months. Overall, it may be four to five months before the final product is delivered to backers:

You can reach us for support through Crowd Supply or by email at dev@agilmine.com. We are also active on the bitcointalk.org forum, under the name arm_race, and on Discord.

For source code and documentation, please see our GitHub repositories. They currently contain our mining host and bitstream file flash programming software. By the end of the campaign, we will also publish the RTL bitstream design source for our mining algorithms, a User’s Guide, schematics, and board-support documents.

If you’re looking for an overview on FPGAs and cryptocurrency, have a look at the following short articles:

All orders will be shipped by Crowd Supply from their facility in the United States. This includes international shipments, for which an additional surcharge will be added at checkout. On average, that surcharge is less than it would cost us to engaging an importer or local distributor, as such services add a hefty markup on top of the product cost for their services, particularly when shipping low volume.

Please note that you will be responsible for any duties or taxes levied by your country, and under no circumstances will Crowd Supply under-declare value, or mark parcels as "gifts" to avoid duties and taxes. For more information about Crowd Supply’s fulfillment and payment polices, please visit the Ordering, Paying, and Shipping page of the Crowd Supply guide.

Manufacturing hardware is always a risky venture. The component market is volatile, especially these days, and the global political situation is unpredictable. For various reasons, demand has been outstripping supply for everything from ceramic capacitors to silicon wafers, which has led to shortages that are extending lead times and raising prices. By choosing a US-based FPGA supplier, we can minimize the potential impact on our manufacturing and delivery plans should US-China trade relations deteriorate.

As described above, we intend to make a few small design changes before our final production run. These include:

While these are all straightforward changes, any design update has the potential, however unlikely, to prolong the development cycle.

Openness, trust, and transparency – while core values to many cryptocurrency enthusiasts – are in short supply within the crypto-mining hardware industry. We would like to change that. Not only through transparent funding and open hardware, but by helping to build a trusted community that can maintain algorithm updates and perhaps even develop new algorithms for the hundreds of thousands of Altcoins that exist.

We are a group of hardware and software engineers who are enthusiastic about cryptocurrency mining. We set up rigs at home and then proceeded to scale them past the point where they became inconvenient and right up to the edge of physical discomfort. So we began researching FPGA miners. Unfortunately, very few dev boards can deliver the power required by mining algorithms, so we didn’t have much luck. We did, however, have quite a lot of experience in the semiconductor industry – on both the hardware and the software sides of the business – so we decided to build our own.

One thing we love about open design, open source software and crowdfunding is the way in which they facilitate direct communication between engineers and their users. We want to bring that dynamic to the world of cryptocurrency mining, but we need your help to do it!

"Hardware startup Agilemine has developed the UltraMiner FPGA cryptocurrency mining board, which they claim has double the speed and four times the energy efficiency of GPU rigs, and is cheaper and more flexible than ASIC platforms."

"Pensada para su uso en aplicaciones de alto rendimiento, esta placa FPGA dispone de soporte para las principales plataformas software de escritorio del mercado."

Produced by Agilmine, LLC in Oregon, USA and Iowa, USA.

Sold and shipped by Crowd Supply.

Developer Edition. Includes with a 16nm Xilinx Kintex UltraScale+ KU30 FPGA, support for PCIe x4 Gen 3, 100 GPIOs, a North Bridge (40x40 mm) passive heatsink, and a MicroUSB cable

We are group of experienced engineers who are enthusiastic about building cryptocurrency mining devices that are open and trustworthy.

Open hardware USB true random number generator

An MCU + eFPGA dev kit with 100% vendor-supported open source tools that fits inside your USB port

An open video development board in a PCI express form factor that supports overlaying content on encrypted video signals. Let's bring open video to the digital age!