Jul 10, 2017

Project update 7 of 10

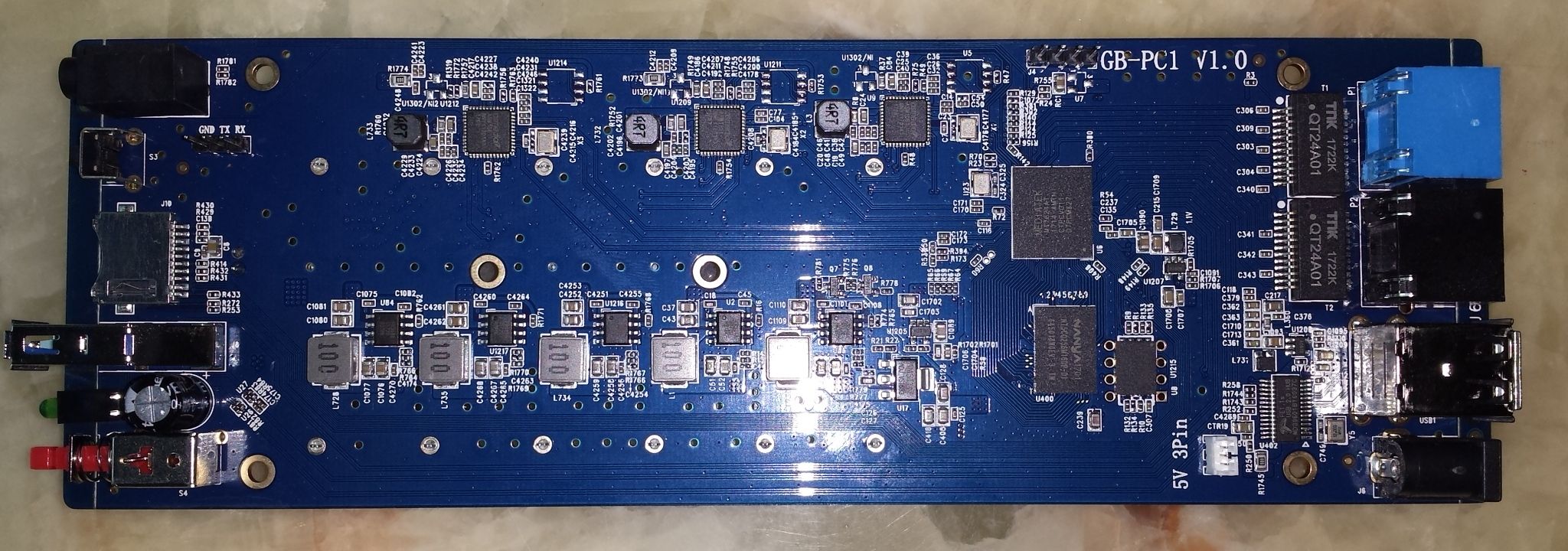

Overclocked Pre-production Units

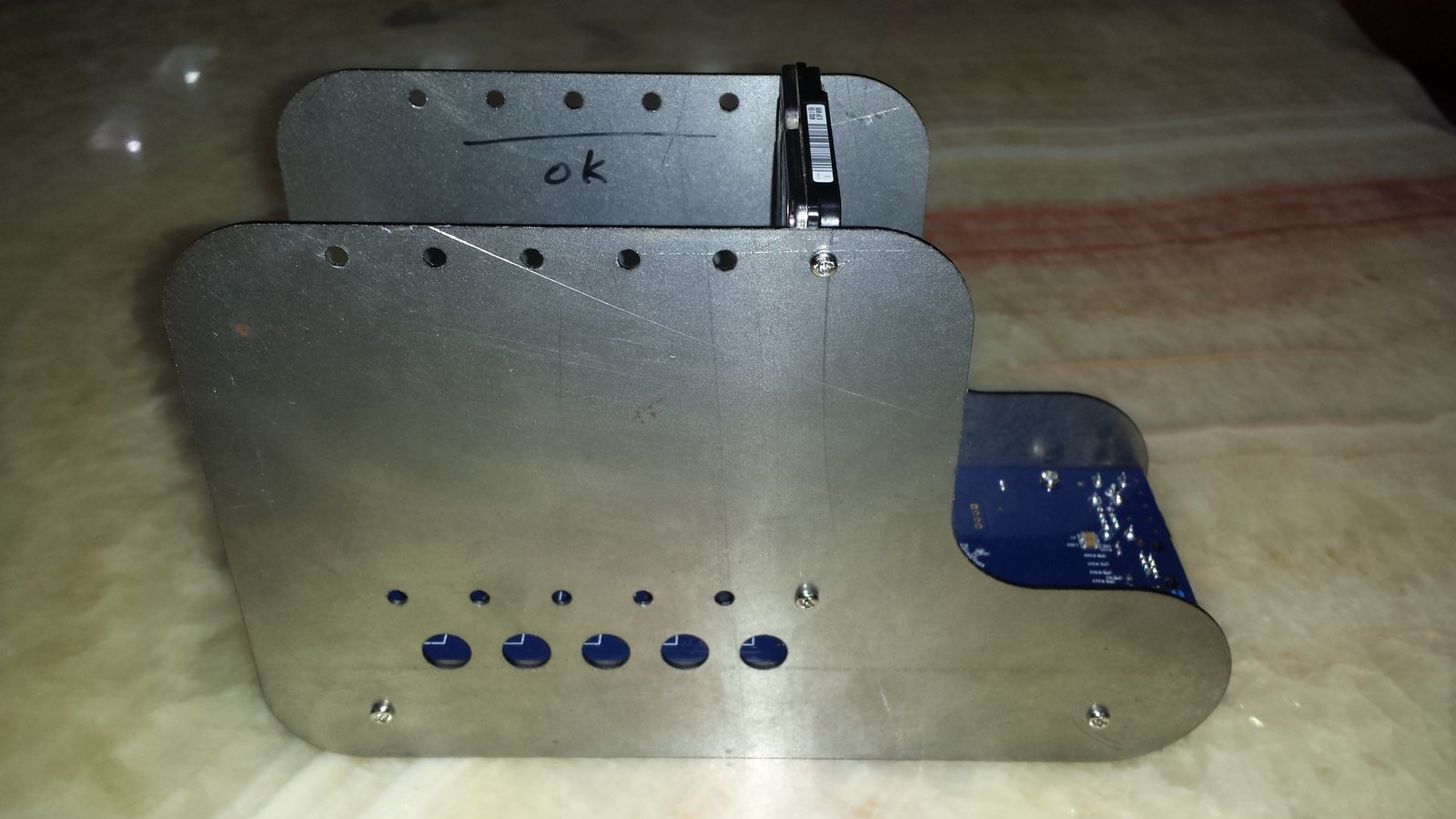

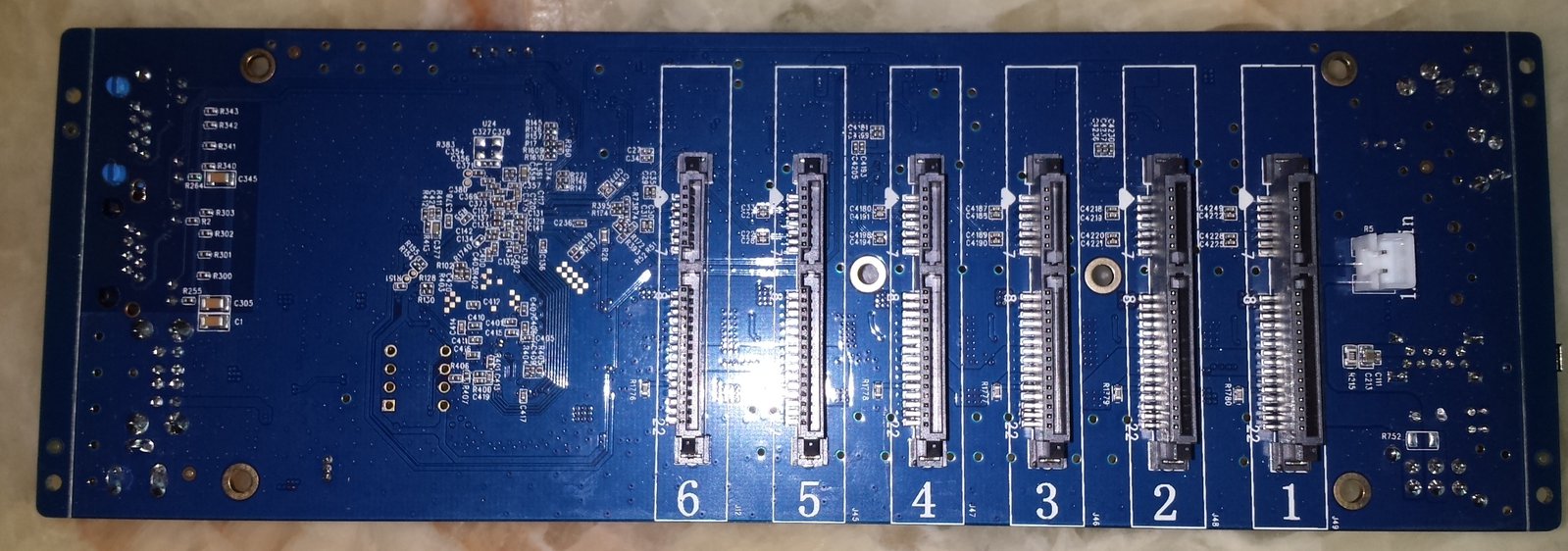

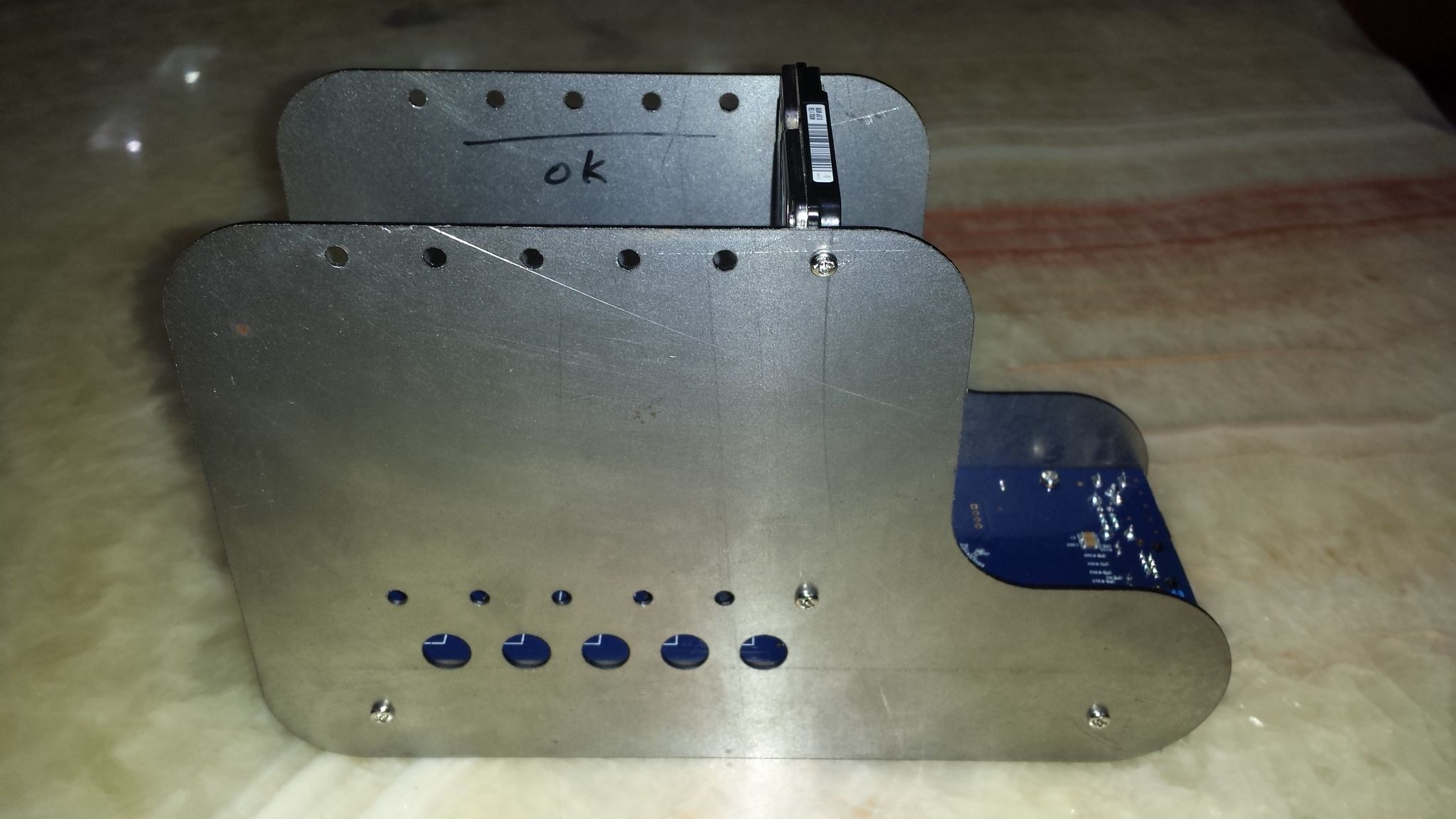

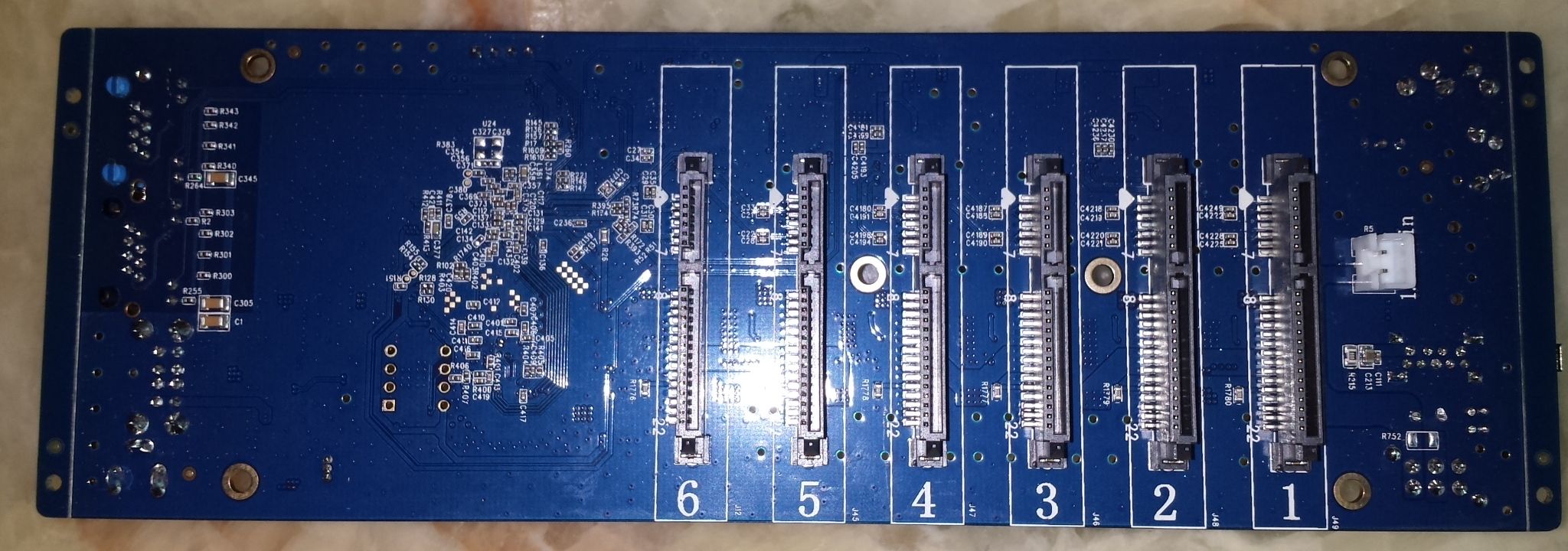

We have two pre-production NiuBi Personal Cloud 1 (NB-PC1) units up and running (overclocked, no less)! Check out the following images. As you can see, the pre-production units have inexpensive, unfinished, steel side plates — the aluminum side plates went off to be anodized earlier today. Production assembly of the PCBs starts tomorrow.

Overclocking and Benchmarks

The two pre-production NB-PC1 units are working well overclocked to 2 GHz. Testing reveals that even higher clock speeds can be achieved.

We get the following benchmarks using openssl, as described at https://wiki.openwrt.org/doc/howto/benchmark.openssl:

openssl speed -multi 4 md5 sha1 sha256 sha512 des des-ede3 aes-

128-cbc aes-192-cbc aes-256-cbc rsa2048 dsa2048

The 'numbers' are in 1000s of bytes per second processed.

type 16 bytes 64 bytes 256 bytes 1024 bytes 8192 bytes

md5 16091.31k 55281.39k 154879.40k 278510.25k 365789.18k

sha1 17060.35k 53599.06k 128982.27k 197786.28k 236047.02k

des cbc 36616.17k 38072.21k 38580.39k 38539.61k 38537.90k

des ede3 13627.75k 13843.48k 13899.01k 13911.72k 13909.19k

aes-128 cbc 50188.57k 54854.81k 56069.29k 56387.24k 56497.49k

aes-192 cbc 43864.69k 47338.69k 48322.56k 48563.20k 48704.17k

aes-256 cbc 39021.53k 41696.85k 42453.76k 42636.97k 42702.17k

sha256 19827.50k 45045.40k 78341.63k 96120.83k 103123.63k

sha512 4002.07k 15991.36k 22059.61k 29743.45k 33109.33k

sign verify sign/s verify/s

rsa 2048 bits 0.021461s 0.000569s 46.6 1757.8

sign verify sign/s verify/s

dsa 2048 bits 0.006466s 0.007229s 154.7 138.3

root@libreCMC:/# cat /proc/cpuinfo

system type : MediaTek MT7621 ver:1 eco:3

machine : GB-PC1

processor : 0

cpu model : MIPS 1004Kc V2.15

BogoMIPS : 1330.38

wait instruction : yes

microsecond timers : yes

tlb_entries : 32

extra interrupt vector : yes

hardware watchpoint : yes, count: 4, address/irw mask: [0x0ffc, 0x0ffc, 0x0ffb, 0x0ffb]

isa : mips1 mips2 mips32r1 mips32r2

ASEs implemented : mips16 dsp mt

shadow register sets : 1

kscratch registers : 0

package : 0

core : 0

VPE : 0

VCED exceptions : not available

VCEI exceptions : not available

VPE : 0

processor : 1

cpu model : MIPS 1004Kc V2.15

BogoMIPS : 1330.38

wait instruction : yes

microsecond timers : yes

tlb_entries : 32

extra interrupt vector : yes

hardware watchpoint : yes, count: 4, address/irw mask: [0x0ffc, 0x0ffc, 0x0ffb, 0x0ffb]

isa : mips1 mips2 mips32r1 mips32r2

ASEs implemented : mips16 dsp mt

shadow register sets : 1

kscratch registers : 0

package : 0

core : 0

VPE : 1

VCED exceptions : not available

VCEI exceptions : not available

VPE : 1

processor : 2

cpu model : MIPS 1004Kc V2.15

BogoMIPS : 1330.38

wait instruction : yes

microsecond timers : yes

tlb_entries : 32

extra interrupt vector : yes

hardware watchpoint : yes, count: 4, address/irw mask: [0x0ffc, 0x0ffc, 0x0ffb, 0x0ffb]

isa : mips1 mips2 mips32r1 mips32r2

ASEs implemented : mips16 dsp mt

shadow register sets : 1

kscratch registers : 0

package : 0

core : 1

VPE : 0

VCED exceptions : not available

VCEI exceptions : not available

VPE : 0

processor : 3

cpu model : MIPS 1004Kc V2.15

BogoMIPS : 1330.38

wait instruction : yes

microsecond timers : yes

tlb_entries : 32

extra interrupt vector : yes

hardware watchpoint : yes, count: 4, address/irw mask: [0x0ffc, 0x0ffc, 0x0ffb, 0x0ffb]

isa : mips1 mips2 mips32r1 mips32r2

ASEs implemented : mips16 dsp mt

shadow register sets : 1

kscratch registers : 0

package : 0

core : 1

VPE : 1

VCED exceptions : not available

VCEI exceptions : not available

VPE : 1

More soon.

Cheers,

Larry and the NiuBi team