Since our last update, we have made a few small improvements to the board and had a second batch of prototypes manufactured. I am happy to say that the minor issues we had with our first batch have now been addressed. Our initial production run, of a couple hundred boards, is currently being manufactured with an estimated lead time of two to four weeks. Production times in China are currently longer than normal, and the company that does our assembly will be closed from the 19th of January until February, but we remain hopeful that we can meet our end-of-January deadline.

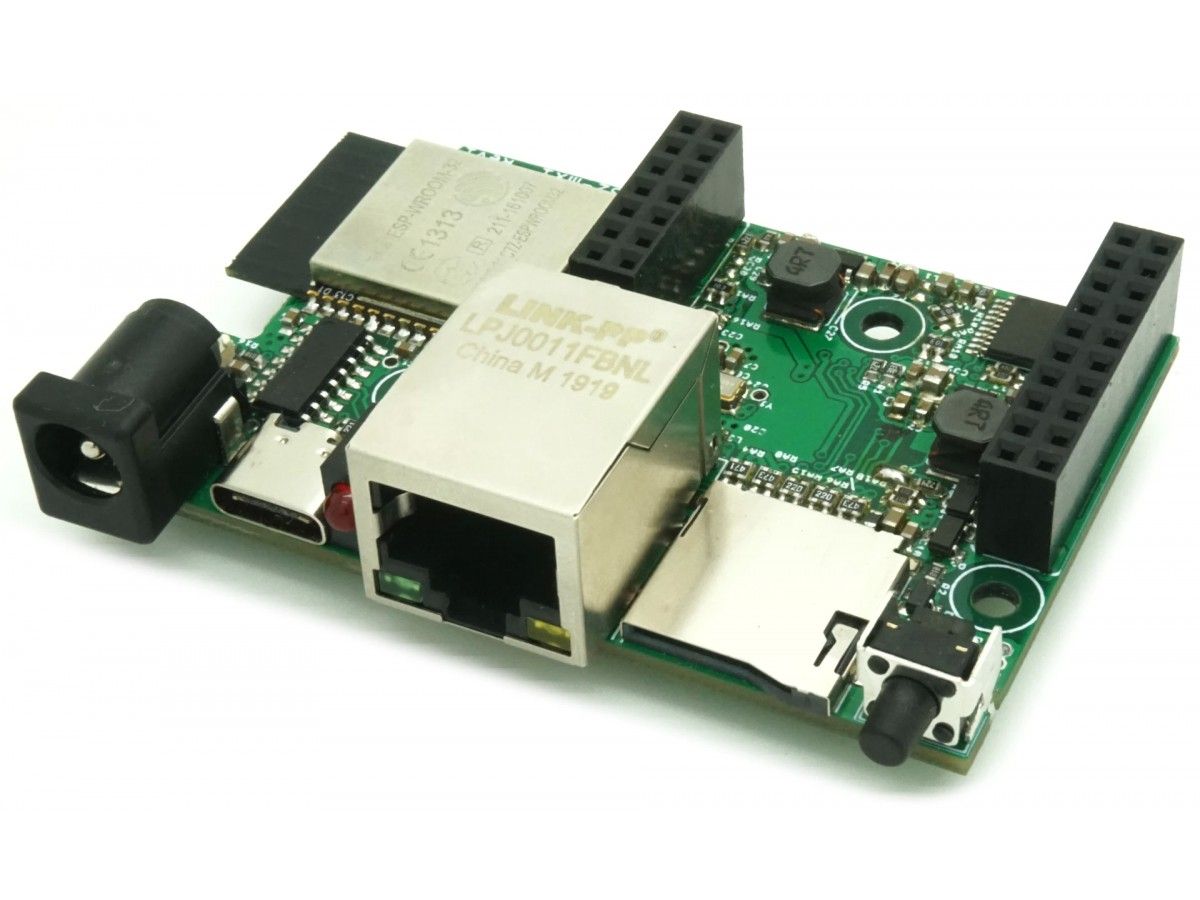

Improvements to esp32MX-E

We had to change some code in the Ethernet API for our first batch of prototypes to ensure that PHY only got reset after the ESP32 started outputting the PHY 50 MHz clock on the IO0 port. We added some PHY clock sensing circuitry that now waits for the output of that clock before releasing the PHY reset. Handled by the secondary STM32F030 microcontroller, this logic requires no additional code in the API and allows esp32MX-E to be used with any software capable of configuring the ESP32 to output the PHY clock on the IO0 line. It also means that no secondary 50 MHz oscillator is required, and no ESP32 pins have to be sacrificed to reset (power) the Ethernet PHY. The ESP32 IO0 pin can now be used for the PHY 50 MHz clock as well as its secondary function of placing the ESP32 into bootloader mode during power up.

We also noticed that a few connectors were too close together and moved them a very short distance. This required only a 0.4 mm increase in the width of the board.

Finally, we added a solder jumper to make the ESP32 reset signal available on the female pin headers.