Project update 1 of 4

SoapySDR and Pothos Support, and More on Hardware Expansion

Thank you to everyone for all the support received in the first few days of the campaign! I have already received a few questions, most of them concerning support for SDR frameworks other than GNU Radio (such as Pothos SDR) or one of the FreeSRP’s most important hardware features: the IO capabilities provided by the expansion port. In this first update, I will try to address these topics.

FreeSRP Now Compatible with SoapySDR and Pothos!

SoapySDR is an SDR interface library which is becoming very popular. There are many interesting applications that use it, like CubicSDR or the Pothos SDR toolkit.

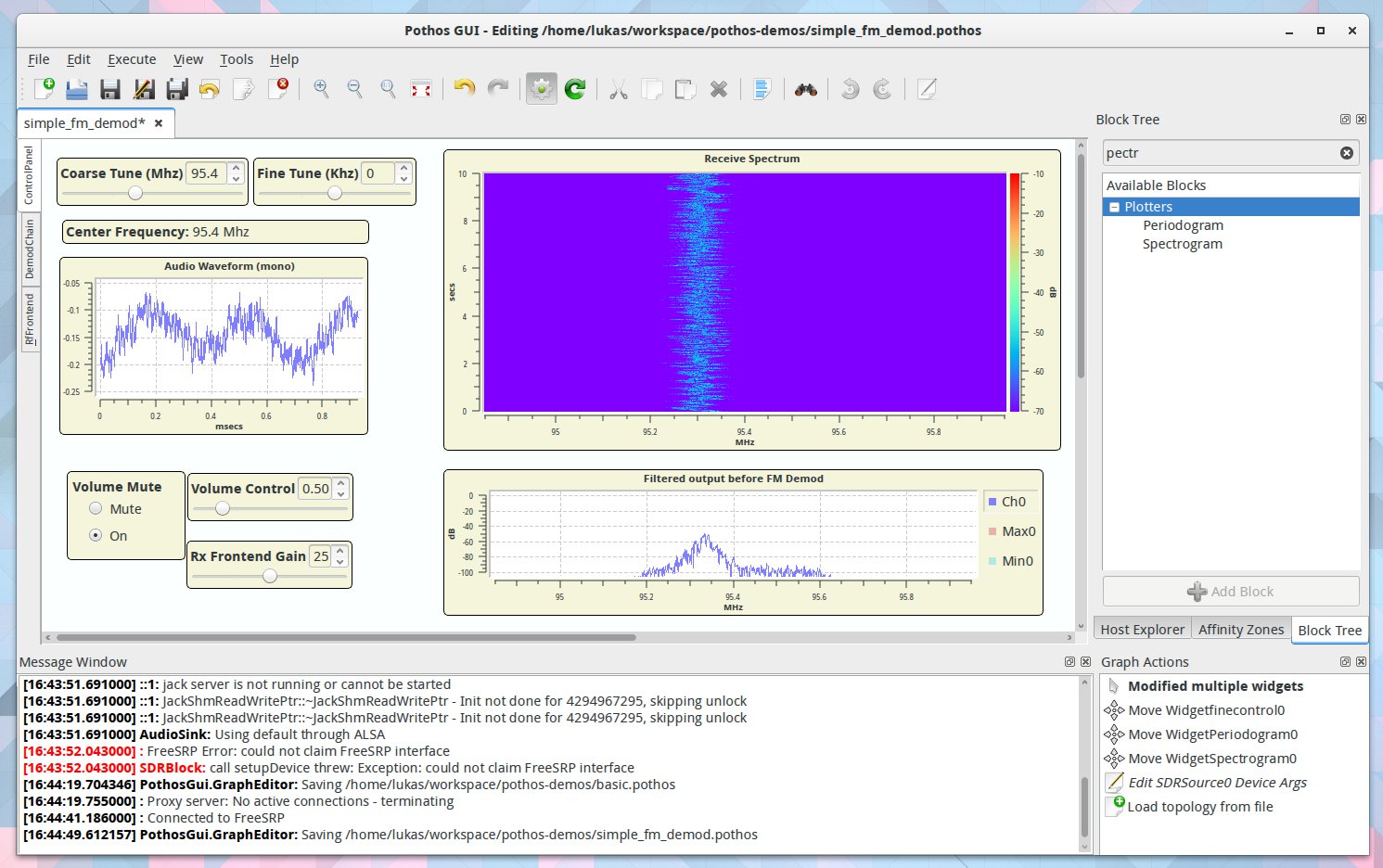

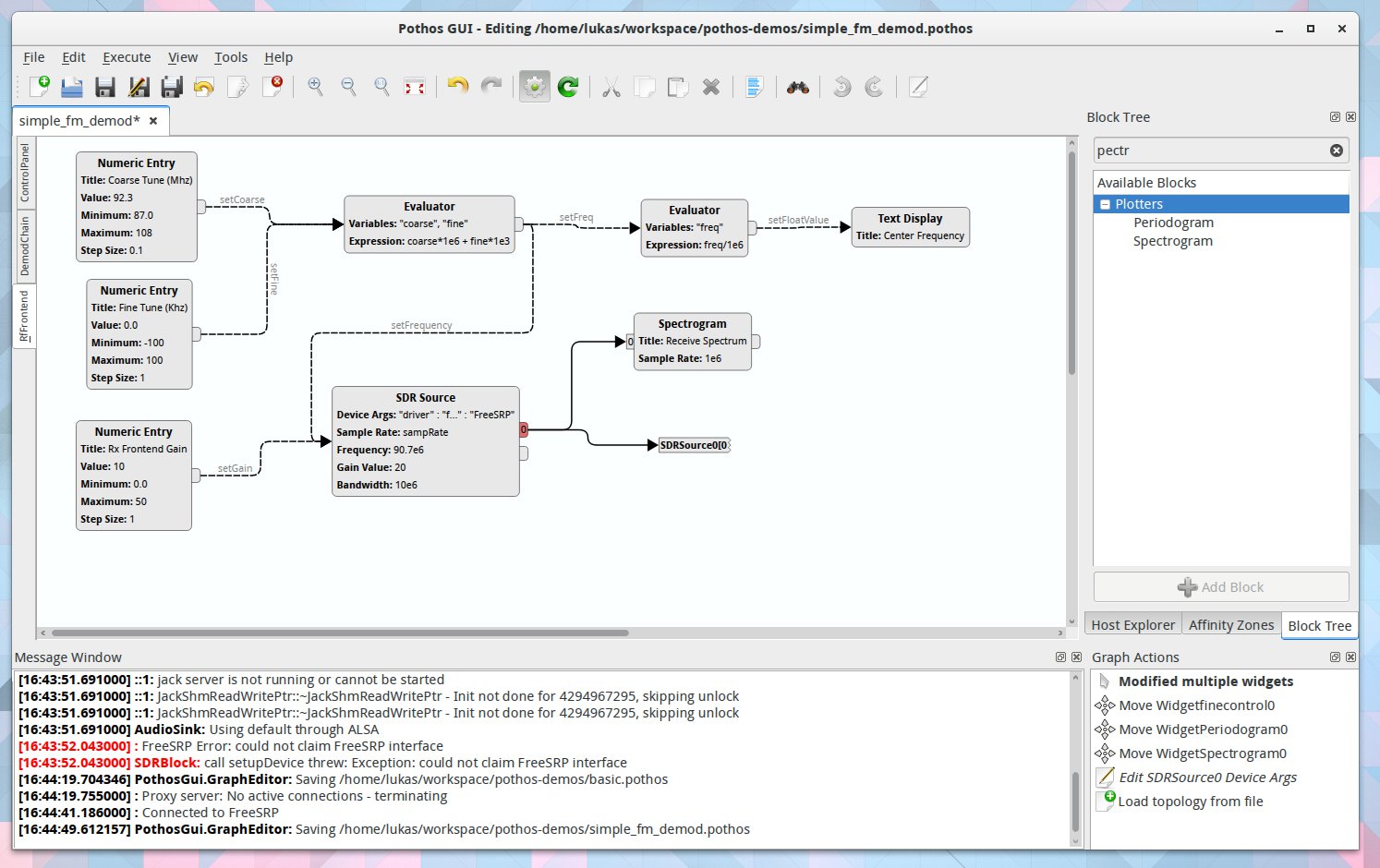

I’m happy to report that I am working on FreeSRP support in SoapySDR and have made considerable progress. For example, it is already working in Pothos, which accesses the FreeSRP through SoapySDR:

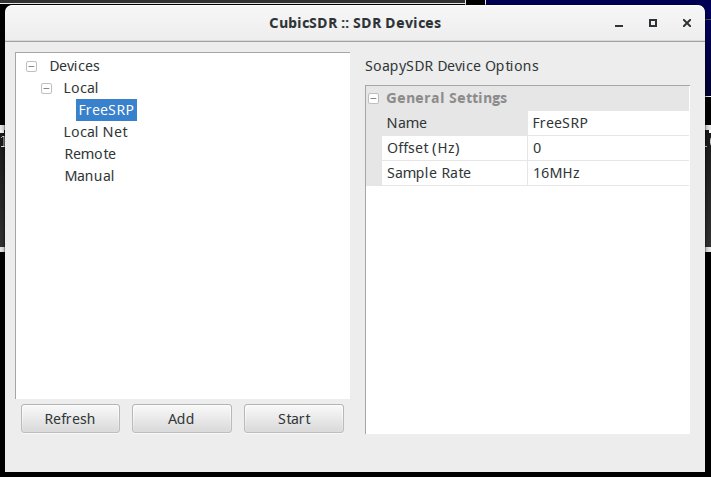

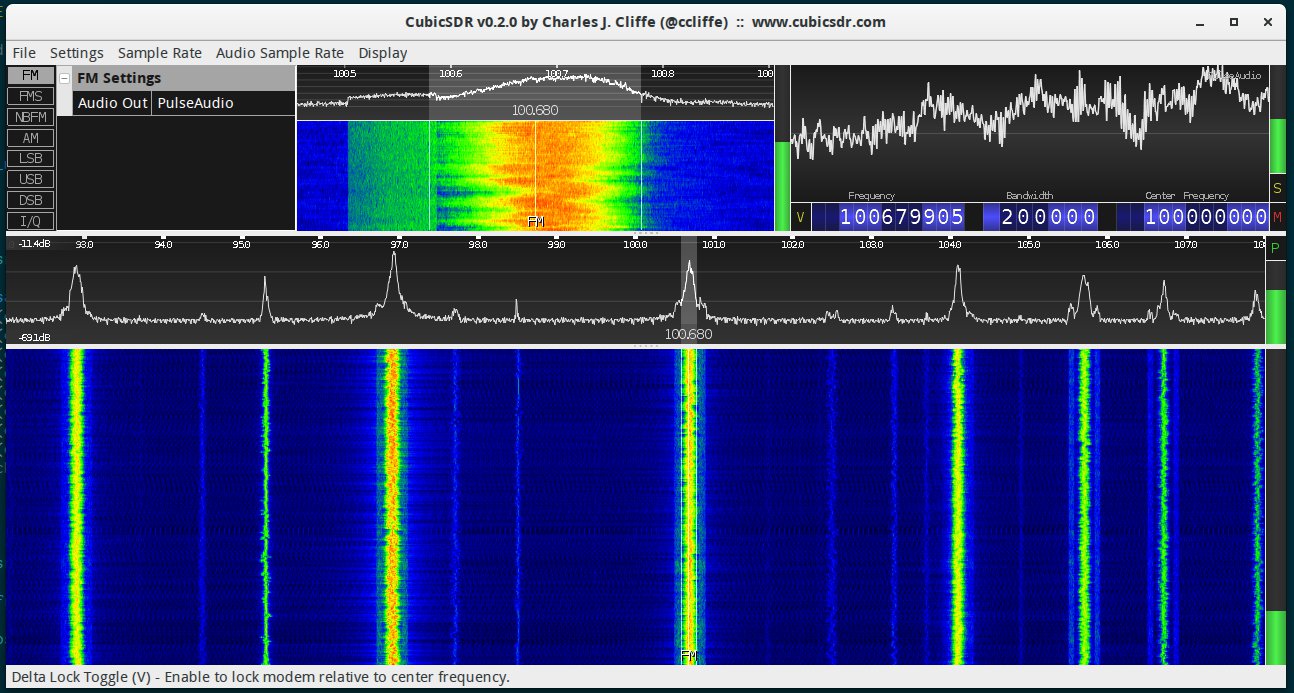

CubicSDR can now also use the FreeSRP through SoapySDR:

The necessary changes to the SoapyOsmo library that had to me made to support the FreeSRP currently live in a custom fork of the main SoapyOsmo repository.

Hardware Expansion Ideas

The hardware expansion capabilities of the FreeSRP are especially compelling for stand-alone or remote operation of the device. That’s why the FreeSRP includes flash memory for configuring the FreeSRP without requiring a connection to a PC.

I’m currently planning to develop several expansion boards for the FreeSRP. Useful add-ons that would be a great first hardware addition are an Ethernet interface and a breakout board providing access to the large number of pins available on the high-speed expansion port.

More Details on the Expansion Ports

The high speed port provides 36 GPIO pins at 1.8V configured to the LVTTL18 standard on the FPGA. Signal pins are separated by ground pins and there is a ground plane connection at the center of the Samtec QSE-040-01-L-D-A connector. Additionally, 1.8V and a connection to the main input voltage (4.45 to 5.25V when powered from USB) are provided.

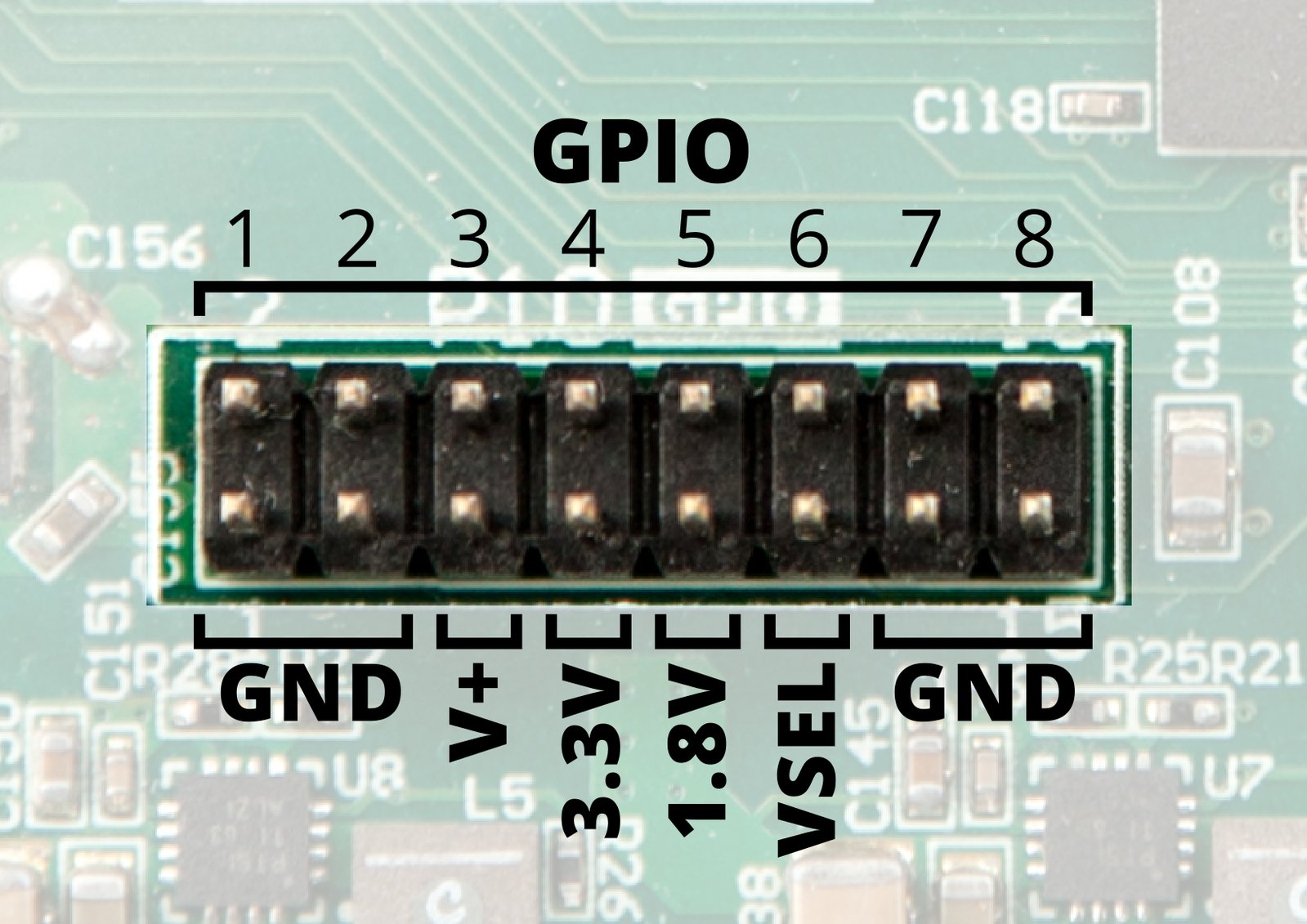

The GPIO pins exposed on the 0.1 inch header have configurable voltage and follow the following pinout:

Here, V+ is connected to the main voltage input, and the GPIO pins operate at the voltage present at VSEL.