Project update 18 of 27

Ready for Serial Production

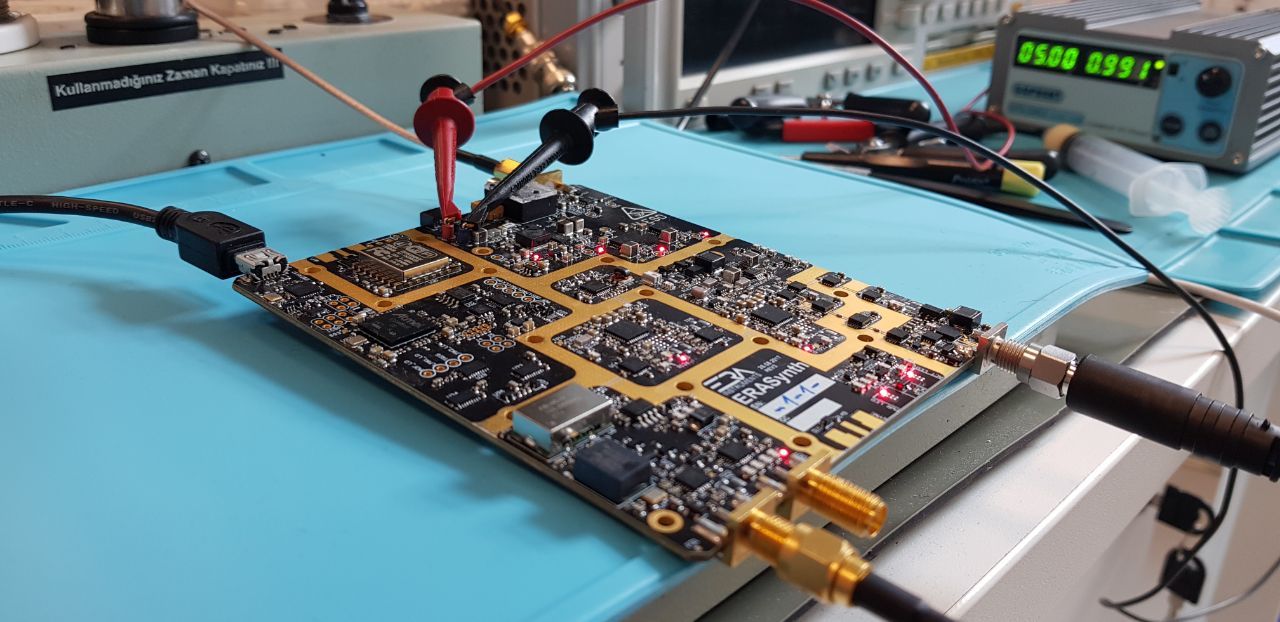

We have been busy testing all the features on ERASynth’s rev3. We are now ready to do serial production.

All PLLs Locked

As you know, we have a triple loop mechanism when generating frequencies 30 MHz - 15 GHz. We were able to lock all three PLLs in a couple of days. For frequencies below, 30 MHz we are using the AD9913 DDS IC. We had some difficulty in getting the DDS path to work. After some debugging we figured that there was a small mistake in the footprint of the level shifter buffer. The DDS IC requires 1.8V logic for control. On the other hand, our MCU (ATSAM3X) provides only 3.3V logic. We used the 74LVCH8T245BQ by NXP to convert the 3.3V signals to 1.8V, but somehow, we ended up messing the pin numbers (the level shifter has a rather weird pin number order). We could just use simple resistors to divide the signals. Anyways, I guess Murphy’s law manifested itself in every stage of the project. Nonetheless, we used budge wires and some resistive dividers to get around the problem and did the testing of DDS path. We corrected the footprint and ordered the rev3.1 of the PCB. It should arrive in a couple of weeks.

Getting the Modulations Work

We spent 80% of our recent time trying to test and debug the modulation functionality. If you had checked out our schematics on the GitHub repo, you would notice we have a narrow-band FM and a wide-band FM. For narrowband FM, we are using a DAC to modulate the VCXO. For wideband FM, we are using a summer OPAMP together with a DAC in the main PLL’s loop filter. We were able to get both FM mods working.

What is Next?

We ordered the final final PCB :). We will call it rev3.1 since it fixes only a very minor error. We will buy the loop filter components in tape and reel. Loop filters usually require some optimization, that is why for the sample run, we used the caps from our cap kits. As for delivery, we should be able to deliver all of the units by Jan 22.

ERA Team Moving to a Larger Office…

Our 20 m2 office has no longer enough space for us. We will move to a new 110 m2 office soon. We are waiting for the previous tenants to move out.