Project update 4 of 12

Integer Boundary Spurs

Integer Boundary Spurs

When we designed ERASynth Micro, we had to optimize the cost. Initially we were planning on using a triple loop PLL architecture similar to its predecessor ERASynth. Later we decided to use a dual loop architecture for two main reasons:

- To keep the final device cost below $250.

- To be able to power it using a USB 2.0 port.

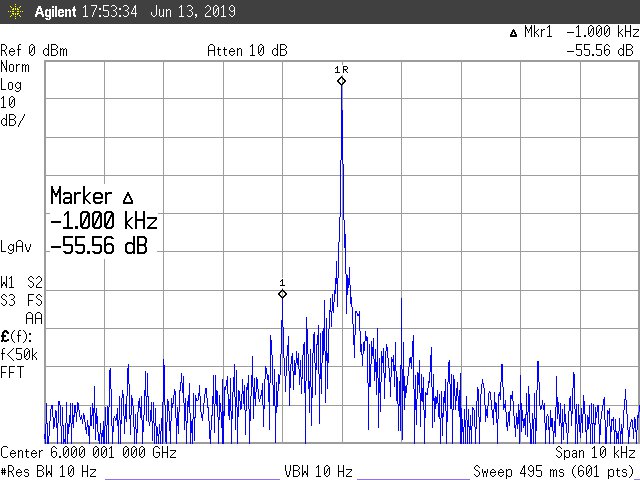

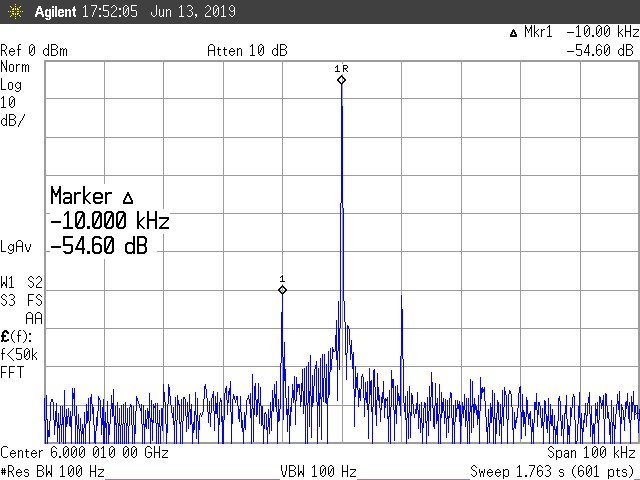

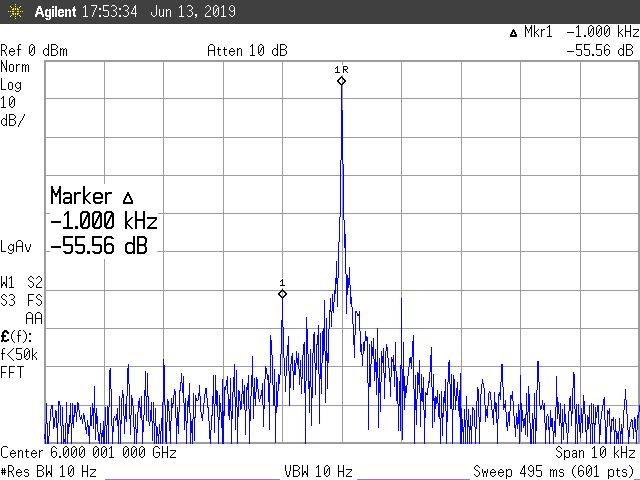

So, we decreased the loop count to two and were able to realize the above goals. However, there were some trade-offs. With a dual loop PLL, we had to operate the main PLL in fractional mode. Fractional PLLs exhibit very large spurious artifacts when output frequency is close to an integer multiple of the PFD rate. We did a few tests to see IBS performance of LMX2572 which is the main PLL IC in ERASynth Micro. The results were surprisingly good. In fact LMX2572 performs better than its big brother LMX2594 when it comes to integer boundary spurs. Please see the following images for test results: